摘要: 锁存器芯片74LS373的中文资料介绍:引脚图及功能、逻辑电路真值表、工作原理、及应用电路图。74LS373是三态输出的八D锁存器,共有54S373和74LS373两种线路。当三态允许控制端 OE 为低电平时,Q0~Q7为正常逻辑状态,可用来驱动负载或总线。当 OE 为高电平时,Q0~Q7 呈高阻态,既不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

74LS373是三态输出的八D锁存器,共有54S373和74LS373两种线路。373 的输出端 Q0~Q7 可直接与总线相连。当三态允许控制端 OE 为低电平时,Q0~Q7为正常逻辑状态,可用来驱动负载或总线。当 OE 为高电平时,Q0~Q7 呈高阻态,既不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

G为数据打入端:当G为“1”时, 锁存器输出状态(1Q~8Q)同输入状态(1D~8D);当G由“1”变“0”时,数据打入锁存器中。

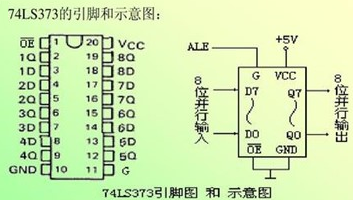

74LS373引脚图如下:

74LS373引脚功能如下:

D0-D7数据输入端,QE三态允许控制端,Q0-Q7输出端

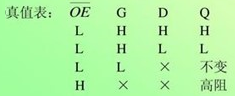

L--低电平;

H--高电平;

X--不定态;

Q0--建立稳态前Q的电平;

G--输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。图中OE--使能端,接地。

当G=“1”时,74LS373输出端1Q-8Q与输入端1D-8D相同;

当G为下降沿时,将输入数据锁存。

a. 1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);

b. 当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态。

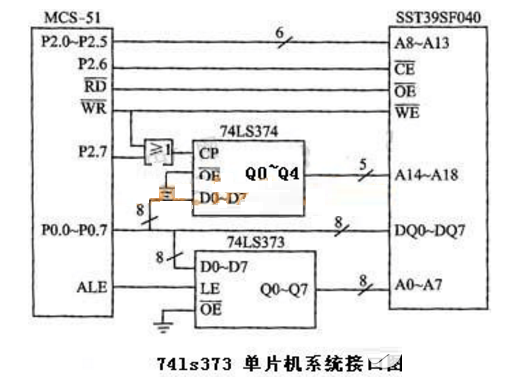

锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。 当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。51单片机的ALE信号可以直接与74LS373的C连接。 74ls373与单片机接口:1D~8D为8个输入端。1Q~8Q为8个输出端。G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。

在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。输出允许端OE接地,表示输出三态门一直打开。

74LS373在单片机扩展系统中的典型应用电路图

当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端G为高电平时,输出Q0-Q7的状态与输入端D1-D7状态相同;当G发生负的跳变时,输入端D0-D7 数据锁入Q0-Q7。51单片机的ALE信号可以直接与74LS373的G连接。在MCS-51单片机系统中,其连接方法如下图所示。其中输入端1D-8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。输出允许端OE接地,表示三态输出门一直导通,可以送出地址信号。

1D-8D为8个输入端;1Q-8Q为8个输出端

社群二维码

关注“华强商城“微信公众号

Copyright 2010-2023 hqbuy.com,Inc.All right reserved. 服务热线:400-830-6691 粤ICP备05106676号 经营许可证:粤B2-20210308